- 您现在的位置:买卖IC网 > Sheet目录2008 > MAX1434ECQ+D (Maxim Integrated Products)IC ADC 10BIT 50MSPS 100-TQFP

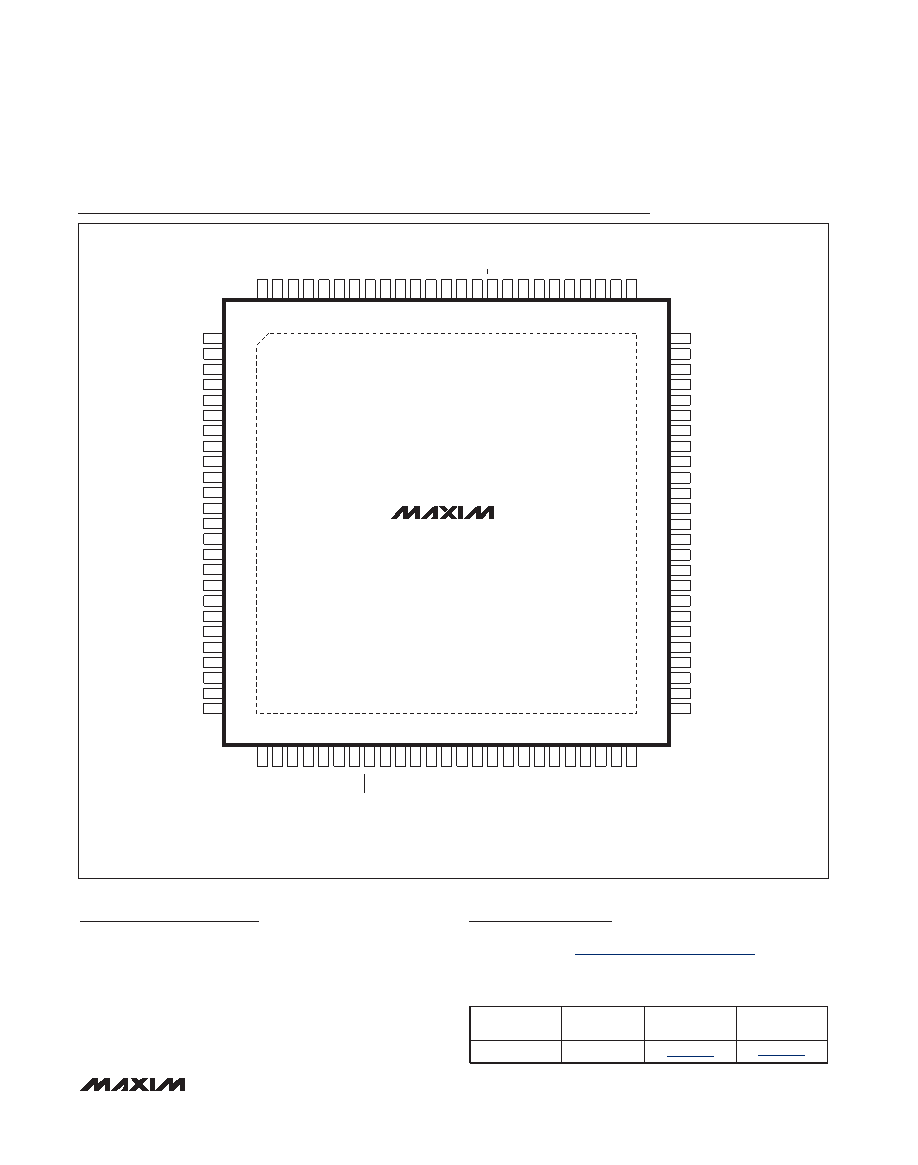

MAX1434

Octal, 10-Bit, 50Msps, 1.8V ADC

with Serial LVDS Outputs

______________________________________________________________________________________

21

N.C.

OVDD

OUT1N

OVDD

OUT2N

OVDD

N.C.

OUT2P

OUT1P

OUT3P

OVDD

FRAMEP

CLKOUTP

CLKOUTN

OUT3N

OVDD

OUT4P

OUT5P

OUT5N

OUT4N

OVDD

FRAMEN

IN1N

GND

IN2P

GND

IN3P

IN3N

GND

IN1P

GND

+

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76

100

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

GND

N.C.

DT

CVDD

N.C.

IN7N

IN7P

GND

IN0N

IN0P

GND

CMOUT

REFADJ

REFIO

GND

REFP

REFN

GND

AV

D

AV

D

AV

D

PLL1

PLL2

PLL3

PD

LVDSTEST

OUT0P

OUT0N

OVDD

N.C.

GND

MAX1434

TOP VIEW

IN2N

AVDD

GND

IN4P

GND

N.C.

IN4N

GND

IN5P

GND

IN6P

IN6N

IN5N

AVDD

GND

CLK

AVDD

OUT7P

OVDD

OUT6N

0VDD

OUT7N

OVDD

OUT6P

TQFP

14mm x 14mm x 1mm

SL

VS/L

VDS

T/B

*EP

*CONNECT EP TO GND

Pin Configuration

Chip Information

PROCESS: BiCMOS

Package Information

For the latest package outline information and land patterns

(footprints), go to www.maxim-ic.com/packages. Note that a

“+”, “#”, or “-” in the package code indicates RoHS status only.

Package drawings may show a different suffix character, but

the drawing pertains to the package regardless of RoHS status.

PACKAGE

TYPE

PACKAGE

CODE

OUTLINE NO.

LAND

PATTERN NO.

100 TQFP-EP

C100E+2

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX1444EHJ+T

IC ADC 10BIT 40MSPS 32-TQFP

MAX1499ECJ+

IC ADC 3 1/2DIG W/LED DVR 32TQFP

MAX152EPP+

IC ADC 8BIT 1UA PWR-DWN 20-DIP

MAX153EPP+

IC ADC 8BIT 1MSPS HI-SPD 20-DIP

MAX154AENG+

IC ADC 8BIT 4CH W/MUX&REF 24-DIP

MAX155AEPI+

IC ADC 8BIT 8CH T/H&REF 28-DIP

MAX157AEUA+

IC ADC 10BIT 108KSPS 2CH 8-UMAX

MAX160CPN+

IC ADC 8BIT UP COMPATIBLE 18-DIP

相关代理商/技术参数

MAX1434ECQ+TD

功能描述:模数转换器 - ADC 10-Bit 8Ch 50Msps 1.8V High Speed ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1434ECQ-D

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1434ECQ-TD

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1434EVKIT

功能描述:数据转换 IC 开发工具 Evaluation Kit for the MAX1434 MAX1436 MAX1437 MAX1438 RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V

MAX1436BECQ

制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述:

MAX1436BECQ+D

制造商:Maxim Integrated Products 功能描述:ADC OCTAL PIPELINED 40MSPS 12-BIT SERL - Rail/Tube

MAX1436BECQ+TD

制造商:Maxim Integrated Products 功能描述:OCTAL 12BIT 40MSPS ADC - Tape and Reel

MAX1436ECQ

制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: